X1 is made for Analog Design, Layout and Verification engineers. It helps teams generate all the verification test case scenarios from a single extraction file.

Analog Verification Has A New Home

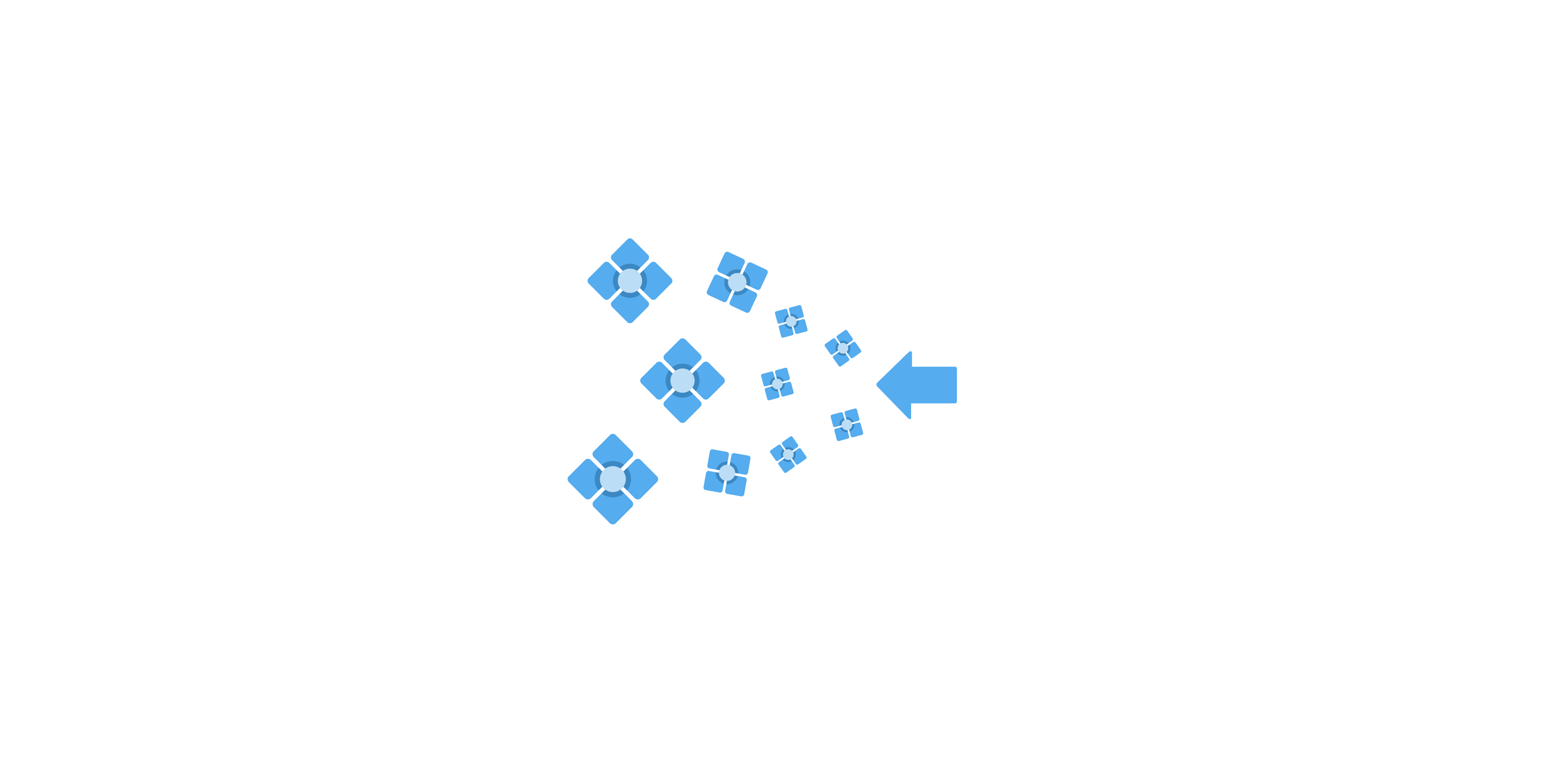

Turn Massive Extractions Into Tiny Verification Scenarios

X1 turns any massive extraction files into verification test scenarios that are both accurate and faster to extract and simulate.

No More

Custom Layouts Multiple Config Views Manual DSPF edits Blind layout iterations Waiting for license availability Hours of extraction configurations Complicated PDK setup

Save 100s of hours of preparing debugging test scenarios for deep sub-micron node layouts

Save your chip from failing and cover all edge-cases you always wanted before tapeout

What is a FACET?

A FACET is a custom extraction file based on your verification intent. A facet preserves the contextual relationship with the rest of the design without any loss in accuracy.

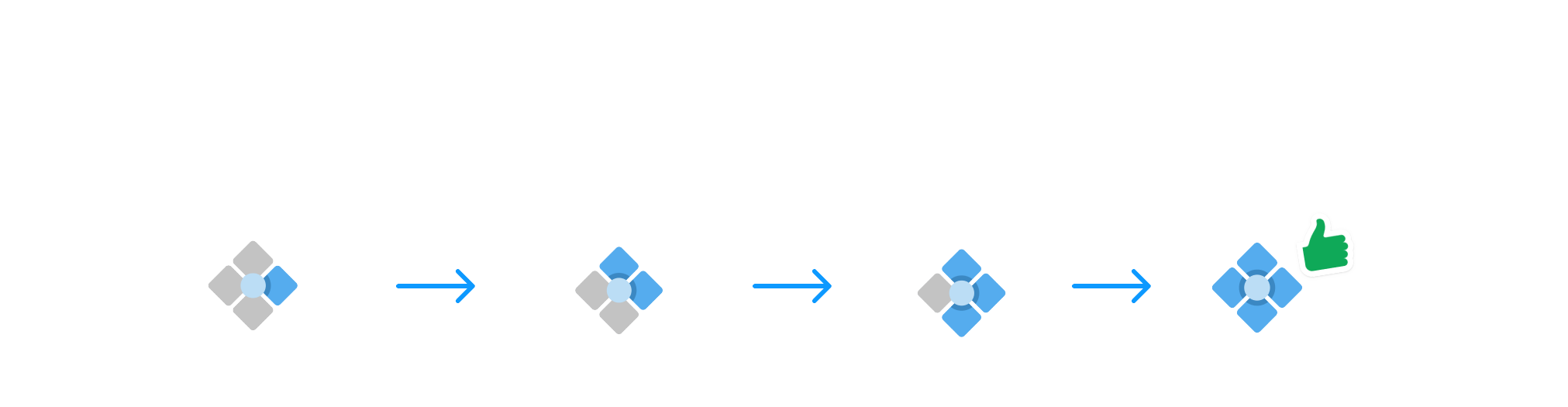

Turn any massive extraction into tiny

verification FACETs in three steps:

1. Zone: Choose the part of your design that requires verification

2. Flavor: Configure each zoned area per your intent and parasitic content

3. Context: Determine the coupling between your verification scenario and

surrounding layout context

Full

Auto

Verification Scenario Configuration

Configure any verification scenario seamlessly in a few clicks

(No more manual steps or custom workarounds)

50x

Extraction Speedup

For every custom extraction generated

10x

Simulation File Reduction

Massive simulation speed improvement without compromising accuracy

Tested on Advanced nodes down to 3nm

shines in all

shines in all

applications

Low power Edge AI

Silicon Photonics

RF, Wireless and IoT

Quantum Computing

PLL, Power management

Energy Harvesting

SerDes, LIDAR

ADCs and DACs

Sensor Interface

Medical Applications

Use Cases

Surgical Debugging

For Any Block

Quick debugging iterations without manual DSPF manipulations OR layout engineers in the loop

Simplify Massive

System Extractions

PSRR

Matching

IR Drop

Dummy Fill Impact

..... & anything you can Imagine you can Verify

Use X1 to reach the optimum netlist size for your verification scenarios, no custom views or re-extractions required. All you need is a verification recipe and in few clicks, you are simulating the parasitics that matters.

Ready to Start?

1. Deploy in minutes

Works with all EDA platforms

Single docker container, Single command setup

On premise deployment with industry-grade security protocols

2. Operate at Scale

GBs of extraction data manipulated in minutes

Work on all PDKs, No Reconfiguration required

3. Win the verification game!

Whatever you Imagine, You can Verify !!

Tested on 180nm-> 3nm

Frequently Asked Questions

X1 tool-agnostic and works on all the standard extraction formats (e.g. DSPF), engineers can add some scripting language to start the tool from inside the EDA platforms commonly used. X1 output files follow the industry standard for all PDKs and can be used directly for simulation.

X1 works on all tech nodes and has already been tested on multiple nodes between 180 down to 3nm (We are always adding more tech nodes!)

This depends on your design sizes. A min of 128GB RAM recommended.

We provide an evaluation period to help you get acquainted with X1 and see where it best fits according to your workflow and methodology.